Introduction

Fan-out control is used in situations where a single PID controller adjusts multiple control elements (e.g., controllers or valves) operating in parallel. Typical applications are:

- Multiple boilers on a common steam header.

- Multiple compressors on a common header.

- Multiple air fan exchangers whose louvers are adjusted by a single temperature controller in the combined outlet.

Each application is discussed below in more detail.

The purpose of this document is to specify the logic required to implement a fan-out application in the Foxboro I/A system.

Boiler Controls

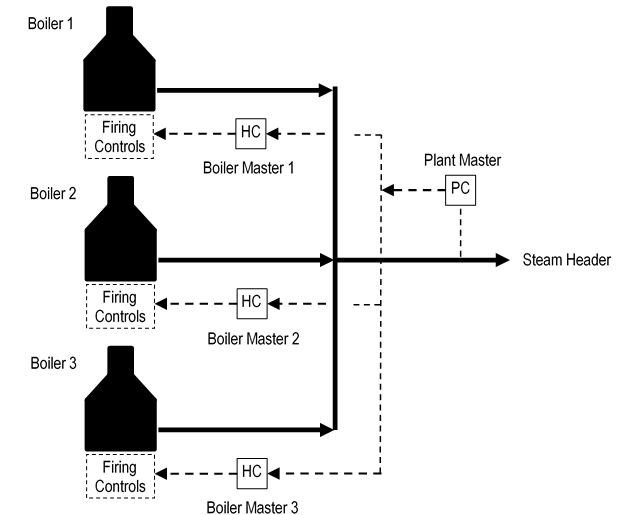

Figure 1 illustrates a typical control scheme for multiple boilers. Each boiler has a bias controller (HC), called a Boiler Master, which applies a bias to the output of a header pressure controller (PC), called a Plant Master. The Boiler Master output goes to the boiler firing controls. The bias allows a boiler to have a different firing rate than the other boilers.

The Plant Master adjusts all Boiler Masters that are in automatic mode. An individual boiler can be disconnected from the Plant Master and base-loaded by putting its Boiler Master in manual mode.

The Boiler Master output can be overridden in the firing controls because of insufficient combustion air or high fuel burner pressure. In this event, the Plant Master must continue controlling the steam header pressure with the other boilers.

Figure 1: Boiler Control Example

Compressor Controls

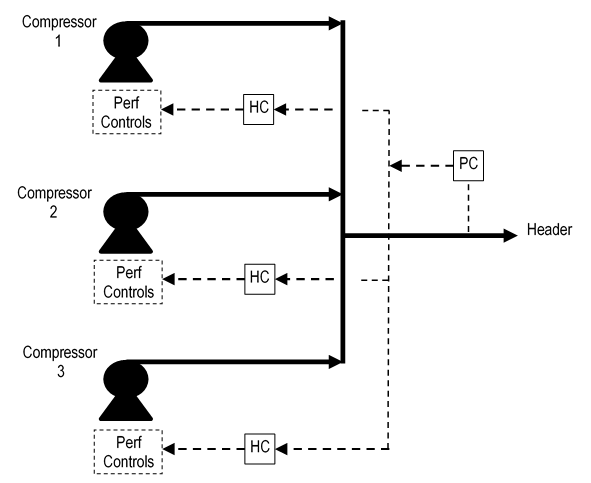

Figure 2 illustrates a typical control scheme for multiple compressors. Each compressor has a bias controller (HC) which applies a bias to the output of a header pressure controller (PC). The HC output goes to the compressor performance controls. The bias allows a compressor to have a different loading than the other compressors, thus providing a means for implementing load balance control.

The PC adjusts all HCs that are in automatic mode. An individual compressor can be disconnected from the PC and base-loaded by putting its HC in manual mode.

The HC output can be overridden in the compressor controls by motor amps (motor-driven compressors) or by low suction pressure. In this event, the PC must continue controlling the header pressure with the other compressors.

Figure 2: Compressor Control Example

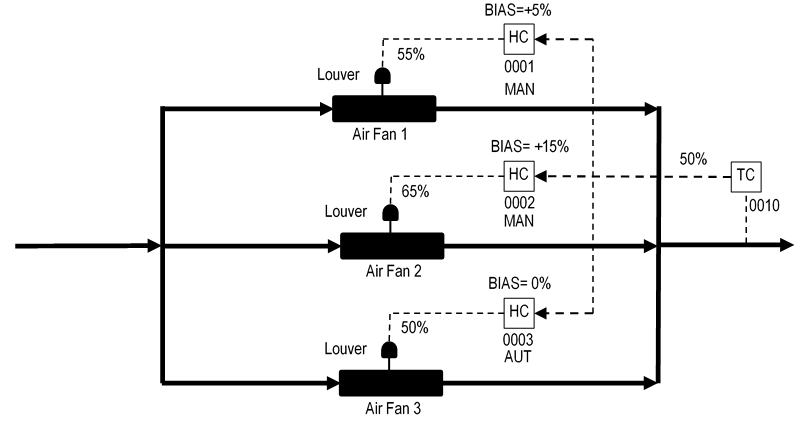

Air Fan Controls

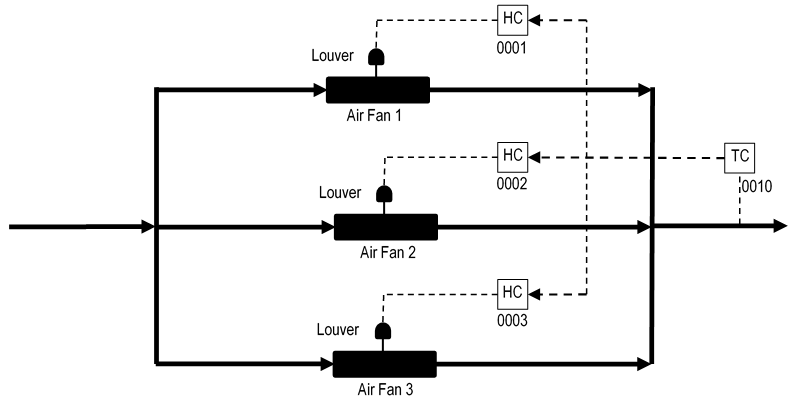

Figure 3 illustrates the control scheme for multiple air fan exchangers. Each air fan louver is adjusted by a HC which applies a bias to the TC output and sends the result on to the louver. The bias allows a louver to be in a different position than the other louvers. This feature is necessary to compensate for different degrees of cooling in the air fans. For example, the bias can be increased for an air fan that is not cooling as much as the others.

The TC adjusts all HCs that are in automatic mode. An individual louver can be disconnected from the TC and adjusted separately by putting its HC in manual mode.

Figure 3: Air Fan Control Example

Primary Controller Adaptive Tuning

The response of the primary controller measurement to a change in its output varies with the number of secondary controllers in control. For example, in the case of the boiler example in Figure 1, a 1% change in the Plant Master output results in three times the response when all three Boiler Masters are in control versus when only one Boiler Master is in control. Likewise, when only two of the three Boiler Masters are in control, the response is twice as large.

Therefore, fan-out applications should include adaptive tuning to automatically adjust the proportional band (PBAND) based on the number of secondary controllers in control. The engineer should enter a PBAND for use when all secondaries are in control. That PBAND should then be automatically reduced for each secondary not in control. The reduction should be based on the relative effect of each secondary on the primary’s measurement. The resulting PBAND should be limited to a minimum value.

Each time the number of secondaries in control changes, the primary should be initialized and the PBAND changed. This feature prevents a bump in the primary output.

Note: a PBAND reduction is actually an increase in gain since gain is the inverse of PBAND.

External Reset Feedback

External reset feedback is used to prevent a primary controller from winding-up when its secondary controller becomes limited, either by hitting an output limit or by being overridden. The feedback signal must be back-calculated based on the forward calculation of the control blocks being used.

For example, the forward calculation for a bias controller is as follows:

HC.OUT = HC.MEAS + BIAS (1)

The feedback calculation, also called the back calculation, is obtained by rearranging Equation 1, where FBK replaces HC.MEAS in the equation:

FBK = HC.OUT – BIAS (2)

The problem with a fan-out application is that each secondary has a separate FBK calculation, but the primary can take only one FBK input. The following examples illustrate this point.

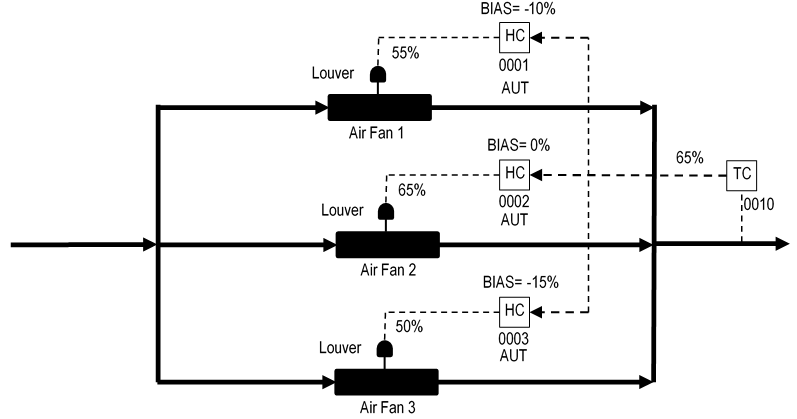

Figure 4: Air Fan Control Example – All HCs in Automatic

External Reset Feedback Examples

In the air fan example in Figure 4, each HC provides a feedback signal to the primary controller (TC0010). We have only one primary controller, so the signals must be selected on some basis to provide a single feedback to TC0010. This can be the highest, the lowest, or the average. If none of the air fans are at a limit, then all three signals are the same and all is well:

HC0001: FBK = 55 – (-10) = 65

HC0002: FBK = 65 – 0 = 65

HC0003: FBK = 50 – (-15) = 65

However, assume that HC0003 is limited at 50% and TC0010 increases its output by 5% (from 65 to 70%). HC0001 output goes from 55 to 60% and HC0002 output goes from 65 to 70%, but HC0003 stays at 50%. The feedback signals now diverge:

HC0001: FBK = 60 – (-10) = 70

HC0002: FBK = 70 – 0 = 70

HC0003: FBK = 50 – (-15) = 65

The average signal (68.3%) lags the true feedback signal (70%), and that divergence will get worse as TC0010 output increases further. At some point, the divergence will be enough to offset the integral action of TC0010 and its control action will stagnate. In this case, the highest feedback signal is best.

A similar problem occurs when TC0010 output needs to be reduced but one of the air fans is at a low limit. In this case, the lowest feedback signal is best, but that conflicts with the previous case.

Best Feedback Logic

The previous discussion indicates that the average feedback signal is not a good choice. That leaves either the highest or lowest signal. The lowest would most likely be from a HC that is not in service (i.e., a closed valve), so the highest signal looks like the best choice. The following logic should be used to determine the feedback signal:

- When at least one HC is in automatic and not limited, the primary controller output should be the feedback signal. This ensures that any HCs that are limited do not interfere with the primary controller integral action.

- When all HCs are either not in control (e.g., in manual) or limited in the same direction, the highest feedback calculation (equation 2) should be the feedback signal.

Controller Initialization – First HC Auto

When all HCs are in manual and one of them is put into automatic, the primary controller’s output should initialize to that HC’s output. Also, the HC’s bias must initialize to zero.

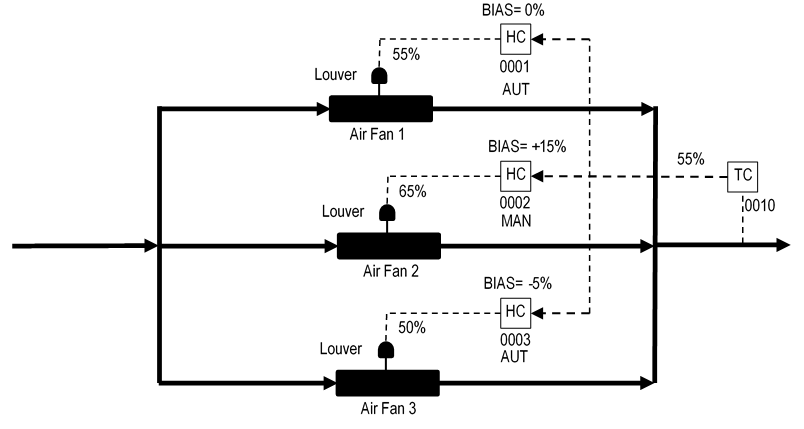

For example, Figure 5 shows a hypothetical set of HC outputs to the louvers. If all HCs are in manual and HC0003 is put into automatic, then TC0010 output should initialize to 50% and HC0003 bias should initialize to zero.

Figure 5: Air Fan Control Example – First HC in Automatic

Controller Initialization – Next HC Auto

When the next HC is put into automatic, the primary controller’s output should initialize to that HC’s output if it is greater than the first HC’s output. Also, the HC biases must initialize to prevent a bump in their outputs.

Figure 6 illustrates this situation. HC0001 is put into automatic after HC0003. TC0010 output initializes to 55% to line up with HC0001 output and HC0003 bias initializes to minus 5% to prevent a bump in its output.

Figure 6: Air Fan Control Example – Next HC in Automatic

Best Initialization Logic

The previous discussion leads to following logic for initializing the controllers:

- When none of the HCs are in control (e.g., all manual), the primary controller should initialize its output to the highest HC output.

- When one of the HCs is put into automatic:

- the primary controller should initialize its output to that HC’s output.

- the HC’s BIAS should initialize to zero.

- When a HC with a higher output is put into automatic:

- the primary controller should initialize its output to that HC’s output.

- the HC’s BIAS should initialize to zero.

- each HC in automatic should re-initialize its BIAS to line up with the new primary controller output.

- When a HC with a lower or equal output is put into automatic, that HC should initialize its BIAS to line up with the primary controller output.

Application Components

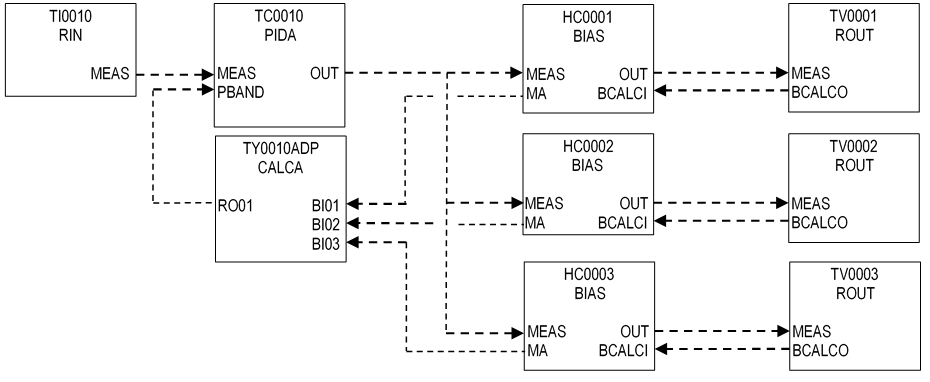

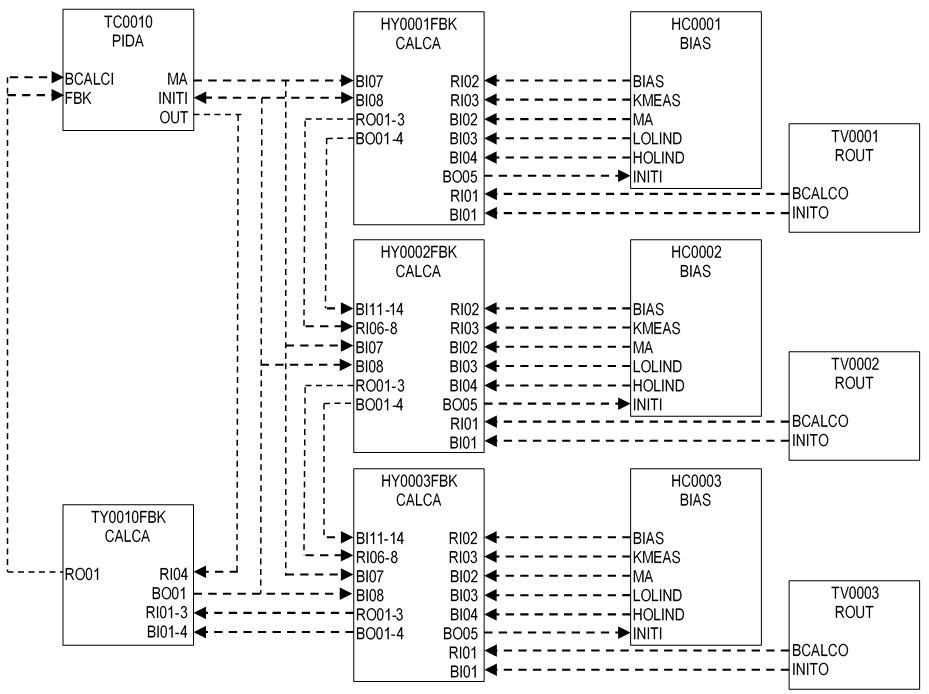

A typical fan-out application contains the following blocks:

- Primary controller (TC0010 in Figure 7).

- Multiple parallel bias controllers (HC0001/2/3 in Figure 7).

- CALCA block containing adaptive tuning logic for the primary controller (TY0010ADP in Figure 7).

- CALCA block containing bias feedback logic for each HC (HY0001/2/3FBK in Figure 8).

- CALCA block containing feedback logic for the primary controller (TY0010FBK in Figure 8).

Figure 7: Block Schematic for Fan-out Controllers

Figure 8: Block Schematic for Fan-out Feedback Logic

Primary Controller Block TC0010

The primary controller TC0010 usually has the following connections:

PBAND = :TY0010ADP.RO01 (Adaptive Tuning Block)

INITI = :TY0010FBK.BO01 (Feedback Logic Block)

BCALCI = :TY0010FBK.RO01

FBK = :TY0010FBK.RO01

Its output is connected to the MEAS of HC0001/2/3 and is in units of %. The output range should allow for the maximum expected bias values. For example, if the maximum expected bias is 50%, then the output range should be -50 to +150.

Bias Controller Block HC0001

The bias controller HC0001 manipulates control valve TV0001 via an ROUT block. The other bias controllers HC0002 and HC0003 are similar. HC0001 has the following connections:

MEAS = :TC0010.OUT (Primary Controller)

INITI = :HY0001FBK.BO05 (Bias Feedback Logic Block)

BCALCI = :TV0001.BCALCO

The block parameters must be set as follows:

HSCI1 = 150 (Same as range of TC0010 output)

LSCI1 = -50

KMEAS = 1.0 (Set based on relative effect of response)

BTRKOP = 1

BTIME = 0.0

Note: The BIAS initialization will not function properly if BTIME is other than 0.0.

Adaptive Tuning Logic Block TY0010ADP

The adaptive tuning logic block is a CALCA block (TY0010ADP). The following connections should be made (Note: Maximum of 6 secondary controllers):

RI01 = :HC0001.KMEAS

RI02 = :HC0002.KMEAS

RI03 = :HC0003.KMEAS

RI04-6 = Other secondary controllers (enter 0 if none)

BI01 = :HC0001.MA

BI02 = :HC0002.MA

BI03 = :HC0003.MA

BI04-6 = Other secondary controllers (enter 0 if none)

Also, the block mode should be locked to automatic:

MA = :TY0010ADP.MA.1

The block parameters must be set as follows:

RI08 = PBAND when all secondaries are in control

M01 = Minimum fraction of PBAND allowed (e.g., 0.3)

Adaptive Tuning Logic Block Steps

STEP01 = IN RI01 ;COMP1 GAIN FACTOR

STEP02 = IN RI02 ;COMP2 GAIN FACTOR

STEP03 = IN RI03 ;COMP3 GAIN FACTOR

STEP04 = IN RI04 ;COMP4 GAIN FACTOR

STEP05 = IN RI05 ;COMP5 GAIN FACTOR

STEP06 = IN RI06 ;COMP6 GAIN FACTOR

STEP07 = ADD 6

STEP08 = OUT M11 ;SUM OF GAIN FACTORS

STEP09 = IN BI01 ;COMP IN CTL

STEP10 = MUL RI01 ;COMP1 GAIN FACTOR

STEP11 = IN BI02 ;COMP IN CTL

STEP12 = MUL RI02 ;COMP2 GAIN FACTOR

STEP13 = IN BI03 ;COMP IN CTL

STEP14 = MUL RI03 ;COMP3 GAIN FACTOR

STEP15 = IN BI04 ;COMP IN CTL

STEP16 = MUL RI04 ;COMP4 GAIN FACTOR

STEP17 = IN BI05 ;COMP IN CTL

STEP18 = MUL RI05 ;COMP5 GAIN FACTOR

STEP19 = IN BI06 ;COMP IN CTL

STEP20 = MUL RI06 ;COMP6 GAIN FACTOR

STEP21 = ADD 6

STEP22 = OUT RO03 ;CURR GAIN FACTOR SUM

STEP23 = DIV M11 ;SUM OF GAIN FACTORS

STEP24 = IN M01 ;MIN PBAND FACTOR

STEP25 = MAX 2

STEP26 = OUT RO02 ;PBAND FRACTION

STEP27 = MUL RI08 ;PBAND ALL RUN

STEP28 = OUT RO01 ;PBAND TO PC

STEP29 = END

Adaptive Tuning Logic Details

Steps 1-8:

The KMEAS values of all secondaries are summed and the sum is stored in M11.

Steps 9-22:

The KMEAS values of all secondaries that are in control are summed and the sum is stored in RO03.

Steps 23-26:

RO03 is divided by M11, the resulting fraction is limited to M01, and the result is stored in RO02.

Steps 27-28:

The fraction in RO02 is multiplied by RI08, which is the PBAND when all secondaries are in control. The result is stored in RO01, which is connected to the primary controller PBAND.

Bias Feedback Logic Block HY0001FBK

The bias feedback logic block HY0001FBK is a CALCA block that provides information to the primary controller feedback logic from the first secondary bias controller HC0001. Because it performs the logic for the first secondary controller, its connections are slightly different than those for the other secondaries:

RI01 = :TV0001.BCALCO (Valve Position)

RI02 = :HC0001.BIAS

RI03 = :HC0001.KMEAS

RI06 = :HY0001FBK.RI06.0.0 (Lock to zero if this is first secondary)

RI07 = :HY0001FBK.RI07.0.0 (Lock to zero if this is first secondary)

RI08 = :HY0001FBK.RI08.0.0 (Lock to zero if this is first secondary)

BI01 = :TV0001.INITO

BI02 = :HC0001.MA

BI03 = :HC0001.LOLIND (HC at low output limit)

BI04 = :HC0001.HOLIND (HC at high output limit)

BI05 = :HY0001FBK.BI05.1 (HC selected in override strategy – lock to 1 if no override)

BI06 = :HY0001FBK.BI06.1 (HC selected in override strategy – lock to 1 if no override)

BI07 = :TC0010.MA

BI08 = :TY0010FBK.BO01

BI09 = :HY0001FBK.BI09.1 (Used for in-service indication – lock to 1 if no indication)

BI11 = :HY0001FBK.BI11.0 (Lock to zero if this is first secondary)

BI12 = :HY0001FBK.BI12.0 (Lock to zero if this is first secondary)

BI13 = :HY0001FBK.BI13.0 (Lock to zero if this is first secondary)

BI14 = :HY0001FBK.BI14.0 (Lock to zero if this is first secondary)

Also, the block mode should be locked to automatic:

MA = : HY0001FBK.MA.1

The block parameters must be set as follows:

M11 = 2

TIMINI = 3

Bias Feedback Logic Block HY0002FBK

The bias feedback logic block HY0002FBK is a CALCA block that provides information to the primary controller feedback logic from the next secondary bias controller HC0002. Its connections are slightly different than those for the first secondary feedback block HY0001FBK (Note: HY0003FBK is similar to HY0002FBK):

RI01 = :TV0002.BCALCO (Valve Position)

RI02 = :HC0002.BIAS

RI03 = :HC0002.KMEAS

RI06 = :HY0001FBK.RO01 (From Logic for Previous Secondary)

RI07 = :HY0001FBK.RO02 (From Logic for Previous Secondary)

RI08 = :HY0001FBK.RO03 (From Logic for Previous Secondary)

BI01 = :TV0002.INITO

BI02 = :HC0002.MA

BI03 = :HC0002.LOLIND (HC at low output limit)

BI04 = :HC0002.HOLIND (HC at high output limit)

BI05 = :HY0002FBK.BI05.1 (HC selected in override strategy – lock to 1 if no override)

BI06 = :HY0002FBK.BI06.1 (HC selected in override strategy – lock to 1 if no override)

BI07 = :TC0010.MA

BI08 = :TY0010FBK.BO01

BI09 = :HY0002FBK.BI09.1 (Used for in-service indication – lock to 1 if no indication)

BI11 = :HY0001FBK.BO01 (From Logic for Previous Secondary)

BI12 = :HY0001FBK.BO02 (From Logic for Previous Secondary)

BI13 = :HY0001FBK.BO03 (From Logic for Previous Secondary)

BI14 = :HY0001FBK.BO04 (From Logic for Previous Secondary)

Also, the block mode should be locked to automatic:

MA = : HY0002FBK.MA.1

The block parameters must be set as follows:

M11 = 2

TIMINI = 3

Bias Feedback Logic Block Steps

STEP01 = AND ~BI01 BI02 ;NOT INIT & AUTO

STEP02 = AND BI09 ;SEC IN SERVICE

STEP03 = OUT M01 ;IN CTL

STEP04 = OR BI11 ;PREV SEC IN CTL

STEP05 = OUT BO01 ;IN CTL TO NEXT SEC

STEP06 = CST

STEP07 = AND ~BI03 M01 ;NOT LO LIM & IN CTL

STEP08 = OUT BO06 ;NOT LO LIM

STEP09 = OR BI12 ;PREV SEC NOT LO LIM

STEP10 = OUT BO02 ;NOT LO LIM TO NEXT SEC

STEP11 = CST

STEP12 = AND ~BI04 M01 ;NOT HI LIM & IN CTL

STEP13 = AND BI05 ;& SELECTED

STEP14 = AND BI06 ;& SELECTED

STEP15 = OUT BO07 ;NOT HI LIM

STEP16 = OR BI13 ;PREV SEC NOT HI LIM

STEP17 = OUT BO03 ;NOT HI LIM TO NEXT SEC

STEP18 = CST

STEP19 = IN M01 ;IN CTL

STEP20 = OSP M11

STEP21 = IN ~M01

STEP22 = OSP M11

STEP23 = OR 2

STEP24 = OR BI14 ;IN CTL CHNG FM PREV SEC

STEP25 = OUT BO04 ;IN CTL CHNG TO NEXT SEC

STEP26 = CST

STEP27 = AND BI07 BI08 ;PRIMARY INIT & AUTO

STEP28 = OUT BO05 ;BIAS INITI

STEP29 = CST

STEP30 = SUB RI01 RI02 ;BCALCO – BIAS

STEP31 = DIV RI03 ;KMEAS

STEP32 = IN M01 ;ELIM IF NOT CTL

STEP33 = MUL 2

STEP34 = OUT RO04 ;FBK

STEP35 = IN RI06 ;FBK PREV SEC

STEP36 = MAX 2

STEP37 = OUT RO01 ;FBK TO NEXT SEC

STEP38 = CST

STEP39 = DIV RI01 RI03 ;BCALCO / KMEAS

STEP40 = IN RI07 ;BCALCO PREV SEC

STEP41 = MAX 2

STEP42 = OUT RO02 ;MAX BCALCO TO NEXT SEC

STEP43 = CST

STEP44 = DIV RI01 RI03 ;BCALCO / KMEAS

STEP45 = IN M01 ;ELIM IF NOT CTL

STEP46 = MUL 2

STEP47 = IN RI08 ;BCALCO IN CTL PREV SEC

STEP48 = MAX 2

STEP49 = OUT RO03 ;MAX BCALCO TO NEXT SEC

STEP50 = END

Bias Feedback Logic Details

Steps 1-5:

The feedback logic needs to know if this secondary is in control. If the ROUT block is not initializing (BI01 = 0) and the bias controller is in auto (BI02 = 1) and the secondary is in service, then the secondary is in control and M01 is set on. BI11 is from the previous secondaries and indicates whether any of them are in control. If BI11 is on or M01 is on then BO01 is set on and passed to the next secondary logic block.

Steps 7-10:

The feedback logic needs to know if this secondary is not at a low limit (BI03=0) and in control (M01=1). The result is stored in BO06. BI12 is from the previous secondaries and indicates whether any of them are not at a low limit. If BI12 is on or BO06 is on, then BO02 is set on and passed to the next secondary logic block.

Steps 12-17:

The feedback logic needs to know if this secondary is not at a high limit (BI04=0), in control (M01=1), and not overridden (BI05=1 and BI06=1). The result is stored in BO07. BI13 is from the previous secondaries and indicates whether any of them are not at a high limit. If BI13 is on or BO07 is on, then BO03 is set on and passed to the next secondary logic block.

Steps 19-25:

The feedback logic needs to know if the in-control status (M01) has changed from the previous execution. If so, or if BI14 is on (indicating that one of the previous secondaries has had a change in its in-control status), then BO04 is set on and passed to the next secondary logic block.

Steps 27-28:

If the primary controller is initializing and this secondary’s bias controller is in auto, then BO05 is set on to initialize the bias controller. This action freezes the bias controller’s output and forces it to initialize its bias to line up with the primary controller’s output.

Steps 30-37:

The feedback signal is calculated using equation 2 and divided by the KMEAS parameter (in the event that KMEAS is a value other than 1.0). If this secondary is not in control (M01=0), then the signal is zeroed out to prevent its use in the final feedback calculation. The result is stored in RO04 and compared to RI06, which contains the highest feedback signal from the previous secondaries. The higher of RO04 and RI06 is stored in RO01 and passed on to the next secondary.

Steps 39-42:

The feedback logic needs to know the highest valve position in terms of the primary controller (by dividing by KMEAS). The result is compared to RI07 (the highest value from the previous secondaries) and the higher value is stored into RO02 and passed to the next secondary logic block.

Steps 44-49:

The feedback logic needs to know the highest valve position of the secondaries that are in control. If this secondary is not in control (M01=0), then the signal is zeroed out to prevent its use in the final feedback calculation. The result is compared to RI08 (the highest value from the previous secondaries) and the higher value is stored into RO03 and passed to the next secondary logic block.

Primary Controller Feedback Logic Block TY0001FBK

The primary controller feedback logic block TY0001FBK is a CALCA block that collects the information from the bias feedback logic blocks. It uses the information to determine the feedback signal for the primary controller. The following connections should be made:

RI01 = :HY0003FBK.RO01 (From the last secondary)

RI02 = :HY0003FBK.RO02 (From the last secondary)

RI03 = :HY0003FBK.RO03 (From the last secondary)

RI04 = :TC0010.OUT (Primary controller output)

BI01 = :HY0003FBK.BO01 (From the last secondary)

BI02 = :HY0003FBK.BO02 (From the last secondary)

BI03 = :HY0003FBK.BO03 (From the last secondary)

BI04 = :HY0003FBK.BO04 (From the last secondary)

Also, the block mode should be locked to automatic:

MA = : TY0010FBK.MA.1

The block parameters must be set as follows:

M11 = 2

M12 = 1

TIMINI = 3

Primary Controller Feedback Logic Steps

STEP01 = IN BI04 ;SEC IN CTL CHNG

STEP02 = OSP M11

STEP03 = OR ~BI01 ;NONE CASCADED

STEP04 = OUT BO01 ;PRIMARY INITI

STEP05 = DON M12

STEP06 = OUT BO02 ;DELAYED INITI

STEP07 = CST

STEP08 = IN ~BI01 ;NONE CASCADED

STEP09 = BIF 12

STEP10 = IN RI02 ;HIGHEST OUTPUT

STEP11 = GTO 24

STEP12 = AND BO01 ~BO02

STEP13 = BIT 23

STEP14 = IN BO02

STEP15 = BIF 18

STEP16 = IN RI03 ;MAX OUT IN CTL

STEP17 = GTO 24

STEP18 = CST

STEP19 = AND BI02 BI03 ;NOT ALL LIM

STEP20 = BIT 23

STEP21 = IN RI01 ;MAX FBK FM SECS

STEP22 = GTO 24

STEP23 = IN RI04 ;PRIMARY OUT

STEP24 = OUT RO01 ;PRIMARY FBK

STEP25 = END

Primary Controller Feedback Logic Details

Steps 1-6:

If any of the secondaries has had a change in control status, then the primary controller must be initialized via BO01. Also, if none of the secondaries are in control, then the primary controller must be initialized. The initialization signal is delayed and stored into BO02 for use later in the logic.

Steps 8-11:

If none of the secondaries are in control, then the highest valve position (RI02) is used for the feedback signal to the primary controller (RO01).

Steps 12-13:

If the primary controller initialization has just begun, then the primary controller’s output (RI04) is used for the feedback signal.

Steps 14-17:

If the primary controller initialization has been happening for a while (BO02=1), then RI03 is used for the feedback signal. RI03 is the highest valve position of the secondaries that are in control.

Steps 19-24:

If at least one of the secondaries is not limited, then the primary controller’s output (RI04) is used for the feedback signal. Otherwise, the highest feedback signal from the bias controllers (RI01) is used for the feedback signal.

Block Execution Order

The block execution order is important to the proper functioning of the application:

- Bias feedback logic blocks (HY0001FBK, HY0002FBK, HY0003FBK)

- Primary controller feedback logic block (TY0010FBK)

- Primary controller adaptive tuning block (TY0010ADP)

- Primary controller (TC0010)

- Bias controllers (HC0001, HC0002, HC0003)

- ROUT blocks for control valves (TV0001, TV0002, TV0003)